- Home

- >

- InfoZone

- >

- electroniques

- >

- La plate-forme Red Pitaya : une instrumentation souple et économique

La plate-forme Red Pitaya : une instrumentation souple et économique

Red Pitaya est une plate-forme de commande et d'instrumentation mono-carte open-source révolutionnaire qui a le potentiel de remplacer de nombreux instruments coûteux, aussi bien dans les laboratoires que pour des applications sur le terrain, mais pour une fraction du prix des équipements de test séparés.

Les premiers équipements de test et de mesure, tels que les oscilloscopes ou les générateurs de signaux, avaient une fonctionnalité fixe et un jeu limité de fonctions. Plus récemment, leurs fournisseurs ont intégrés le traitement numérique des signaux (DSP) pour élargir une gamme de fonctions mieux adaptées à des applications spécifiques. Cependant, la capacité de programmation et de configuration des fonctions de ces instruments a toujours été limitée par leurs fabricants. Actuellement, même avec la plus étendue des gammes de fonctions, la plupart des instruments n'ont pas les fonctionnalités précisément exigées par des projets spécifiques. Ce manque est évident en particulier pour les chercheurs dans les instituts et les universités qui développent des systèmes complexes basés sur des sous-systèmes et/ou des instruments. Dans de tels cas, il est souvent indispensable d'utiliser des instruments à des résolutions plus élevées que celles prévues par les fabricants. Des problèmes d'intégration peuvent surgir dans des systèmes exigeant des retours d'information très rapides. Par exemple s'ils utilisent deux ou plusieurs sous-systèmes d'instrument qui nécessitent des réponses matérielles en temps réel avec une gigue la plus faible possible. Souvent, les interfaces des instruments se révèlent incapables de fournir le niveau requis de performance intégrée.

Red Pitaya

La nouvelle Red Pitaya répond à ces problèmes et facilite le développement économique de nombreuses variantes d'instrumentation à partir d'une seule plate-forme, en conjonction avec un écosystème de développement open-source unique. Lancée grâce à un projet de financement Kickstarter, Red Pitaya est une plate-forme de traitement de signaux open-source, programmable et personnalisable par l'utilisateur, qui combine un équipement basé sur le système sur puce (SoC) Xilinx Zynq®-7010 avec un référentiel open-source d'applications d'instrumentation en ligne.

Le SoC Zynq combine un processeur double cœur ARM® Cortex™-A9 avec une sélection de périphériques, plus la logique d'un réseau de portes programmables in situ (FPGA) Xilinx 7 series. Il sert de fondation à une grande variété d'instruments développés sur des logiciels disponibles dans la bibliothèque d'une communauté d'ingénieurs, connue sous le nom de Bazaar dans le cloud. En outre, le référentiel Backyard de Red Pitaya héberge les outils et les codes de développement open-source nécessaires au développement des applications, avec Spark Center et DesignSpark. Les ingénieurs peuvent partager ces ressources et apporter de nouvelles idées et contributions pour poursuivre le développement des applications Red Pitaya et de nouveaux modules d'extension matériels. L'unité centrale sous Linux prend en charge les périphériques standard, tels qu'Ethernet, USB OTG, stockage Micro-SD et console série USB. Red Pitaya peut être programmée à différents niveaux avec des interfaces logicielles variées, incluant HDL, C/C++ et des langages de script. Des interfaces HTML permettent d'accéder aux fonctionnalités de Red Pitaya avec la plupart des navigateurs, à partir d'une tablette, smartphone ou PC.

Matériel

Outre le Soc Zynq, la plate-forme matérielle offre deux entrées analogiques rapides 14 bits et 125 Msample/s avec des convertisseurs analogiques-numériques Linear Technology ; deux sorties analogiques rapides 14 bits et 125 Msample/s ; quatre entrées analogiques 12 bits et 100ksample/s ; quatre sorties analogiques 12 bits et 100ksample/s ; un port USB et un port Ethernet. La plate-forme est dotée de plusieurs connecteurs d'expansion permettant d'ajouter divers modules d'extension matériels, supportant des ports analogiques ou numériques supplémentaires, ou encore d'autres ressources. De plus, le traitement distribué est rendu possible par le montage en marguerite de plusieurs modules Red Pitaya à l'aide de connecteurs sériels rapides, permettant de construire un système complexe et évolutif, capable de recevoir d'autres entrées et sorties. Les capacités de la plate-forme sont présentées dans la Figure 1.

Figure 1 – Plate-forme Red Pitaya

Un jeu initial de cinq applications open-source est disponible (conçu pour être stocké sur la carte micro-SD embarquée). Il inclut un oscilloscope d'échantillonnage numérique à deux canaux 14 bits et 125-Msample/s ; un analyseur de spectre à deux canaux de 60 MHz avec un affichage graphique en cascade ; un générateur d'ondes de formes aléatoires (ARB) à deux canaux 125 MHz ; un analyseur de réponse en fréquence à deux canaux 60 MHz ; et un régulateur PID (proportionnel intégral dérivé) à deux canaux.

Les fonctions de génération et d'acquisition de signaux à deux canaux 125 Msample/s peuvent être combinées avec un traitement numérique des signaux (DSP) basé sur le FPGA pour former des boucles de feedback matériel en temps réel. Le système intègre aussi plusieurs canaux E/S plus lents de 100 kHz avec plusieurs E/S numériques.

Architecture

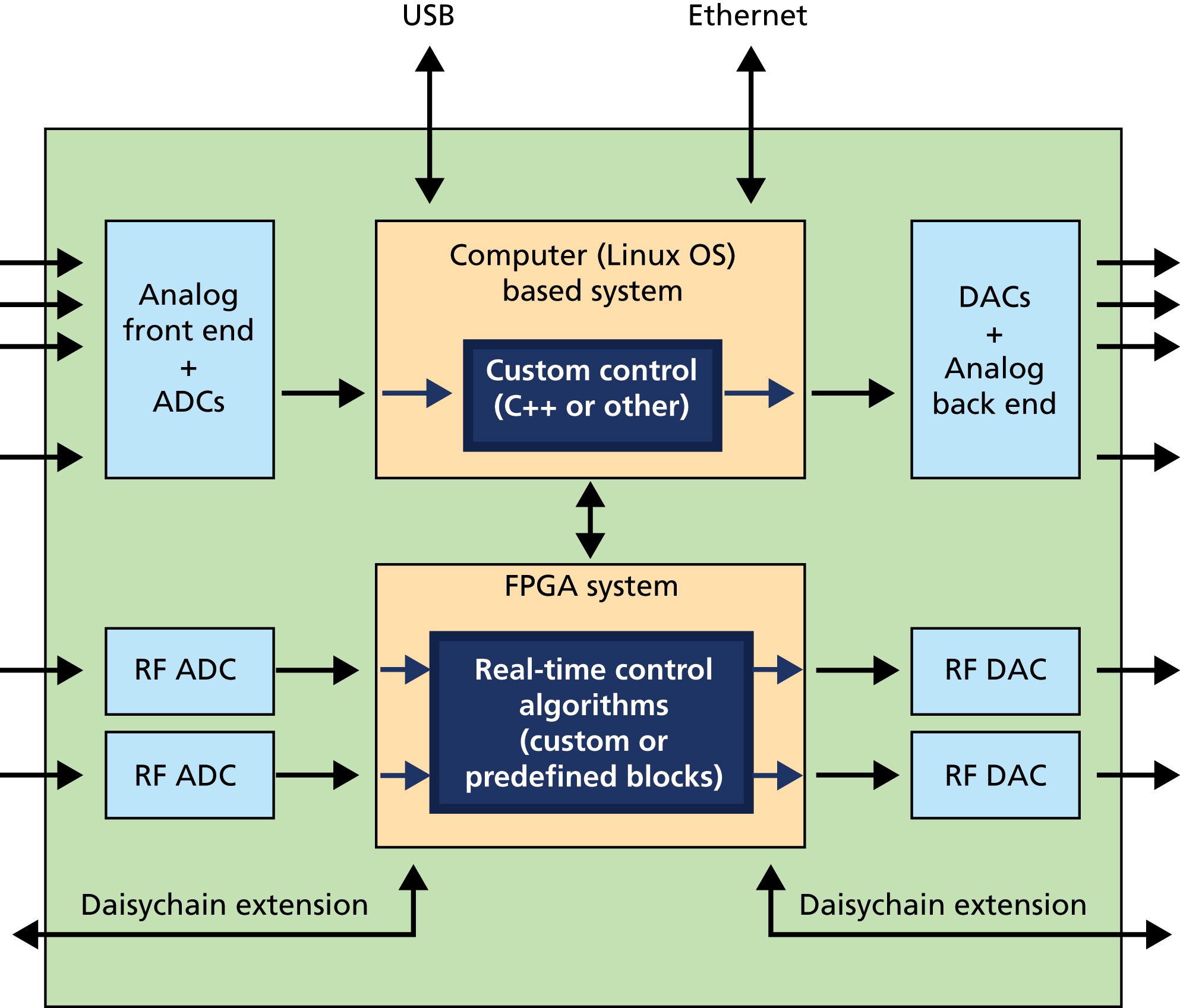

La Figure 2 représente l'architecture du système de traitement de signaux du Red Pitaya avec plusieurs entrées

et sorties analogiques et numériques.

Figure 2 – Architecture système Red Pitaya

La plate-forme suit l'approche basique du traitement de signaux, où tous les éléments spécifiques du système de traitement et de mesure sont concentrés dans le domaine numérique. L'approche doit être aussi simple et générique que possible au niveau de l'électronique analogique front-end et back-end et pour échantillonner le plus tôt possible les signaux à l'aide des convertisseurs analogiques-numériques rapides et les envoyer aux convertisseurs numériques-analogiques aussi tard que possible dans la chaîne de traitement. L'architecture extrêmement numérique de la plate-forme permet de personnaliser le matériel et d'exécuter des opérations diverses sur plusieurs applications. Les possibilités sont seulement limitées par la bande passante de l'électronique analogique front-end et back-end et par les ressources du processeur et du FPGA dans le domaine numérique.

Deux principaux types de chaîne de traitement sont disponibles : La chaîne de traitement de signaux (bande passante de ~50 MHz) qui exploite les capacités de traitement matériel en temps réel extrêmement rapides et à gigue faible des FPGA. La deuxième chaîne (elle aussi à ~50 kHz) supportée par l'unité centrale, capable d'exécuter un système d'exploitation temps réel (RTOS).

Partitionnement du DSP

Presque tous les instruments sont confrontés au challenge de la réduction de vastes quantités de données générées par des échantillons bruts, par exemple un schéma d'oscilloscope de seulement 1000 points, ou le tracé des fréquences d'un analyseur de spectre. Par conséquent, la réduction des données d'entrées de l'instrument sur ses sorties est le rôle principal de la fonction de traitement numérique des signaux.

La combinaison d'un réseau de portes programmables in situ (FPGA) et d'une unité centrale autorise donc une importante liberté pour partitionner les éléments du traitement des signaux. En général, le FPGA gère les opérations DSP simples mais ultra-rapides, alors que l'unité centrale est la spécialiste des opérations de procédures aléatoirement complexes, mais plus lentes. Bien que le développement des outils FPGA ait largement progressé au cours des dernières années, l'écriture de logiciels procéduraux pour des unités centrales restent encore la plus facile des options. Cette liberté de partitionnement apporte un avantage supplémentaire : la capacité de prototyper rapidement un système totalement fonctionnel, même si sa performance reste limitée. L'exécution de la plus grande partie du DSP sur l'unité centrale permet de prototyper des démonstrations dès le début du projet de développement. Elle autorise le report sur le FPGA de la « partie performance » du DSP pour obtenir un produit final ayant la même fonctionnalité, mais avec une performance accrue. La Figure 3 présente un exemple de partitionnement des algorithmes DSP entre le FPGA et l'unité centrale.

Figure 3 – Partitionnement des algorithmes DSP entre le FPGA et l'unité centrale

La séparation peut varier pendant le cycle de développement. Mais comme le traitement DSP est partagé, les données partiellement traitées doivent être transférées entre le FPGA et l'unité centrale ou réciproquement. La vitesse du bus joue donc un rôle important pour éviter d'introduire des latences de traitement.