Kit de démarrage FPGA Altera

- Code commande RS:

- 787-7037

- Référence fabricant:

- DK-START-5AGXB3N

- Marque:

- Altera

Ce produit n’est plus distribué

- Code commande RS:

- 787-7037

- Référence fabricant:

- DK-START-5AGXB3N

- Marque:

- Altera

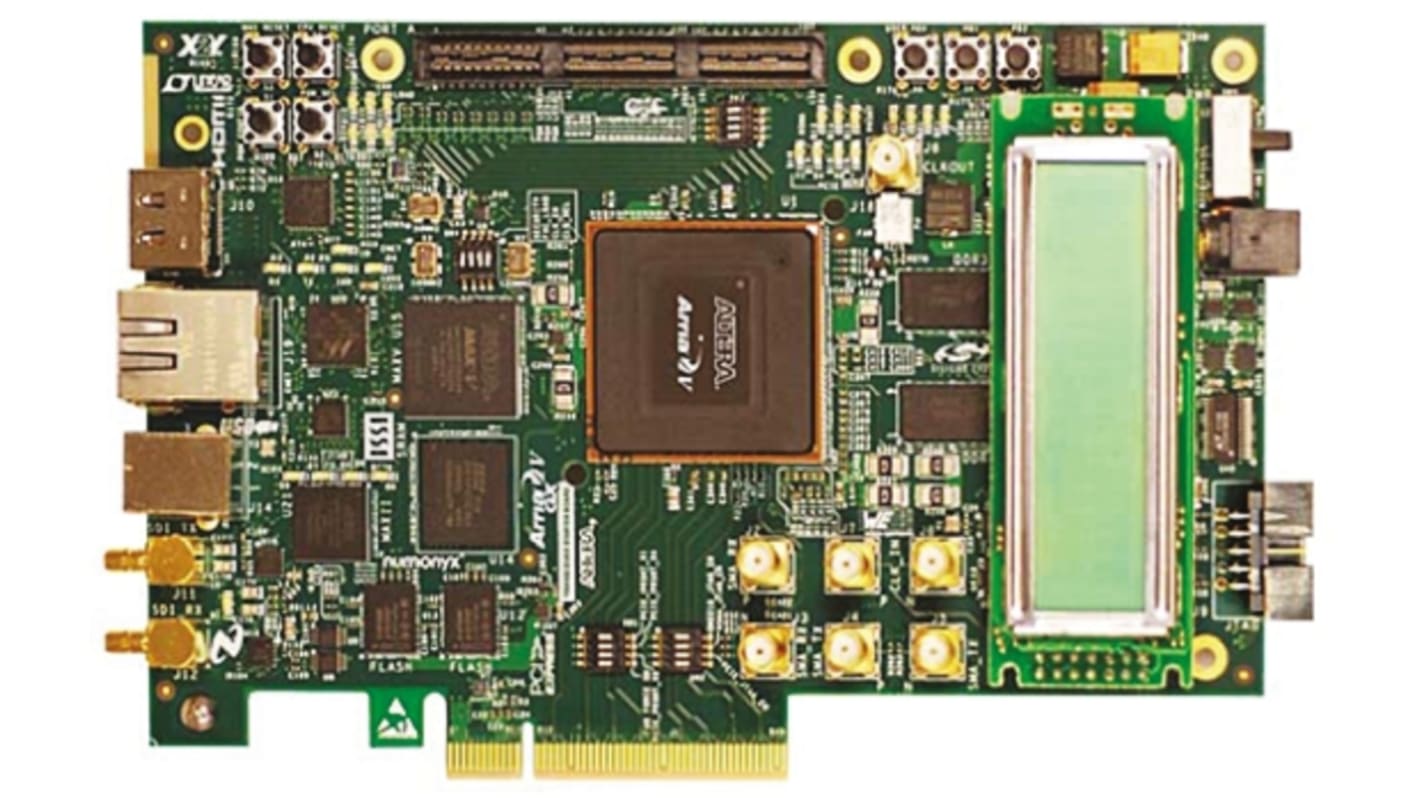

Kit de démarrage Arria V GX FPGA, Altera

Le kit de démarrage Altera Arria® V GX FPGA comprend tout le matériel et les logiciels nécessaires au développement immédiat d'applications FPGA économiques. Il est doté de connecteurs d'interface multimédia haute définition (HDMI) et d'interface numérique en série (SDI).

FPGA

Arria V GX 5AGXFB3H4F35C5N

Contrôleur de système : circuit MAX V 5M2210ZF256C4N

Interface graphique utilisateur du moniteur de puissance

Convertisseur analogique à numérique (ADC) avec huit canaux

Rail de puissance non isolé

Mode Fast passive parallel (FPP) x16 via le chargeur Flash parallèle (PFL)

Registres de commande et d'état

USB-Blaster II intégré : circuit MAX II EPM570GM100C4N

HDMI 1.3 TX

4 x XCVR, 2,7 Gbps (max par le translateur de niveau) et connecteur Tx HDMI d'horloge Tx 270 MHz

Translateur de niveau HDMI STMicroelectronics STHDLS101T

Translateur de niveau XCVR PCML 1,5 V <-> Niveau TMDS

Homologations DDC et HPD <-> Niveau compatible HDMI

Canal de données jusqu'à 2,7 Gbps ; compatible HDMI 1.3

Canal d'horloge jusqu'à 270 MHz ; suffisant pour prendre en charge une vitesse de transmission de 2,7 Gbps

Spécification HDMI : période d'horloge = 10x d'UI

SDI 3G

Rebouclage Tx/Rx XCVR

2 x connecteurs SMB (le câble n'est pas inclus dans le kit)

Jusqu'à 2,97 Gbps

Utilise le variateur/récepteur National Semiconductor LMH0384SQ/LMH0303SQx

Nécessite 148,5 MHz et 148.35 MHz à XCVR refclk pour respectivement se conformer aux normes US et EU

Utiliser VCXO pour régler et verrouiller la fréquence CDR récupérée

HSMC

8 x XCVR jusqu'à 6,375 Gbps

Non conforme au brochage HIP PCI Express (PCIe)

4 x CMOS

8 x interface de différentiel Tx et 9 x interface de différentiel Rx utilisant les canaux Tx/Rx dédiés

2 x pointage d'entrée de signalisation différentielle à basse tension (LVDS)

2 x pointage de sortie différentiel

Bus I2C

JTAG

Courant minimum : 2 A @ 3,3 V, 1 A @ 12 V

Domaine d'horloge dédié à partir du générateur d'horloge Si 5338 pour xcvr refclk

Rebouclage HSMC avec interface graphique utilisateur BTS

SMA

Canal Tx/Rx XCVR

Entrée d'horloge LVPECL

Sortie d'horloge LVPECL

Domaine d'horloge dédié à partir du générateur d'horloge Si 5338 pour xcvr refclk

DDR3 SDRAM

Micron MT41J64M16LA-15E DDR3 SDRAM 8M x 16 x 8

Deux circuits : 2 x 16 largeur = x32

Interface graphique utilisateur SDRAM DDR3 BTS utilisant Uniphy et le contrôleur hautes performances (HP) II

SSRAM

512 K x 36, ISSI IS61VPS51236A 18 Mo

Adresse ou données partagées avec Flash

E/S d'utilisateur

Afficheur LCD à caractères

4 x interrupteur DIP

3 x boutons poussoirs

4 LED

Configuration

Mode FPP x16

Double Flash 512 Mbit Numonyx PC28F512P30BF (52 MHz fMAX)

Embase JTAG

USB Blaster II intégré

Microcontrôleur Cypress CY7C68013A sous USB PHY 2.0

Circuit MAX II

Ethernet

10/100/1000 Base-T

Connecteur RJ-45, LED intégrée pour l'état de la liaison

Ethernet Marvell PHY 88E1111

Nécessite une horloge de 50 MHz de CLKIN

Arria V GX 5AGXFB3H4F35C5N

Contrôleur de système : circuit MAX V 5M2210ZF256C4N

Interface graphique utilisateur du moniteur de puissance

Convertisseur analogique à numérique (ADC) avec huit canaux

Rail de puissance non isolé

Mode Fast passive parallel (FPP) x16 via le chargeur Flash parallèle (PFL)

Registres de commande et d'état

USB-Blaster II intégré : circuit MAX II EPM570GM100C4N

HDMI 1.3 TX

4 x XCVR, 2,7 Gbps (max par le translateur de niveau) et connecteur Tx HDMI d'horloge Tx 270 MHz

Translateur de niveau HDMI STMicroelectronics STHDLS101T

Translateur de niveau XCVR PCML 1,5 V <-> Niveau TMDS

Homologations DDC et HPD <-> Niveau compatible HDMI

Canal de données jusqu'à 2,7 Gbps ; compatible HDMI 1.3

Canal d'horloge jusqu'à 270 MHz ; suffisant pour prendre en charge une vitesse de transmission de 2,7 Gbps

Spécification HDMI : période d'horloge = 10x d'UI

SDI 3G

Rebouclage Tx/Rx XCVR

2 x connecteurs SMB (le câble n'est pas inclus dans le kit)

Jusqu'à 2,97 Gbps

Utilise le variateur/récepteur National Semiconductor LMH0384SQ/LMH0303SQx

Nécessite 148,5 MHz et 148.35 MHz à XCVR refclk pour respectivement se conformer aux normes US et EU

Utiliser VCXO pour régler et verrouiller la fréquence CDR récupérée

HSMC

8 x XCVR jusqu'à 6,375 Gbps

Non conforme au brochage HIP PCI Express (PCIe)

4 x CMOS

8 x interface de différentiel Tx et 9 x interface de différentiel Rx utilisant les canaux Tx/Rx dédiés

2 x pointage d'entrée de signalisation différentielle à basse tension (LVDS)

2 x pointage de sortie différentiel

Bus I2C

JTAG

Courant minimum : 2 A @ 3,3 V, 1 A @ 12 V

Domaine d'horloge dédié à partir du générateur d'horloge Si 5338 pour xcvr refclk

Rebouclage HSMC avec interface graphique utilisateur BTS

SMA

Canal Tx/Rx XCVR

Entrée d'horloge LVPECL

Sortie d'horloge LVPECL

Domaine d'horloge dédié à partir du générateur d'horloge Si 5338 pour xcvr refclk

DDR3 SDRAM

Micron MT41J64M16LA-15E DDR3 SDRAM 8M x 16 x 8

Deux circuits : 2 x 16 largeur = x32

Interface graphique utilisateur SDRAM DDR3 BTS utilisant Uniphy et le contrôleur hautes performances (HP) II

SSRAM

512 K x 36, ISSI IS61VPS51236A 18 Mo

Adresse ou données partagées avec Flash

E/S d'utilisateur

Afficheur LCD à caractères

4 x interrupteur DIP

3 x boutons poussoirs

4 LED

Configuration

Mode FPP x16

Double Flash 512 Mbit Numonyx PC28F512P30BF (52 MHz fMAX)

Embase JTAG

USB Blaster II intégré

Microcontrôleur Cypress CY7C68013A sous USB PHY 2.0

Circuit MAX II

Ethernet

10/100/1000 Base-T

Connecteur RJ-45, LED intégrée pour l'état de la liaison

Ethernet Marvell PHY 88E1111

Nécessite une horloge de 50 MHz de CLKIN

fourni avec

Cartes filles pour boucle et embase de débogage, câble USB, câble vidéo SMB 75 Ω, câble Ethernet, licence pour l'édition du kit de développement (DKE) du logiciel Quartus II (plate-forme Windows uniquement).

Un FPGA est un dispositif à semi-conducteurs composé d'une matrice de blocs logiques configurables (CLB) connectés par des interconnexions programmables. L'utilisateur détermine ces interconnexions en programmant la mémoire SRAM. Un CLB peut être simple (portes AND, OR, etc.) ou complexe (un bloc de RAM). Le FPGA permet d'apporter des modifications à une conception même après le soudage du dispositif sur un circuit imprimé.

Attribut | Valeur |

|---|---|

| Technologie de logique programmable | FPGA |

| Classification du kit | Kit de démarrage |

| Dispositif | 5AGXFB3H4F35C5N |

| Nom du kit | Arria V GX |