- Code commande RS:

- 906-3924

- Référence fabricant:

- DK-DEV-10M50-A

- Marque:

- Altera

1 pour livraison dès le lendemain (stock France)

2 Sous 2 jour(s) (stock Europe)

Ajouté

Prix pour la pièce

214,66 €

HT

257,59 €

TTC

| Unité | Prix par unité |

| 1 - 1 | 214,66 € |

| 2 - 4 | 209,16 € |

| 5 + | 203,93 € |

- Code commande RS:

- 906-3924

- Référence fabricant:

- DK-DEV-10M50-A

- Marque:

- Altera

Documentation technique

Législation et Conformité

- Pays d'origine :

- TW

Détail produit

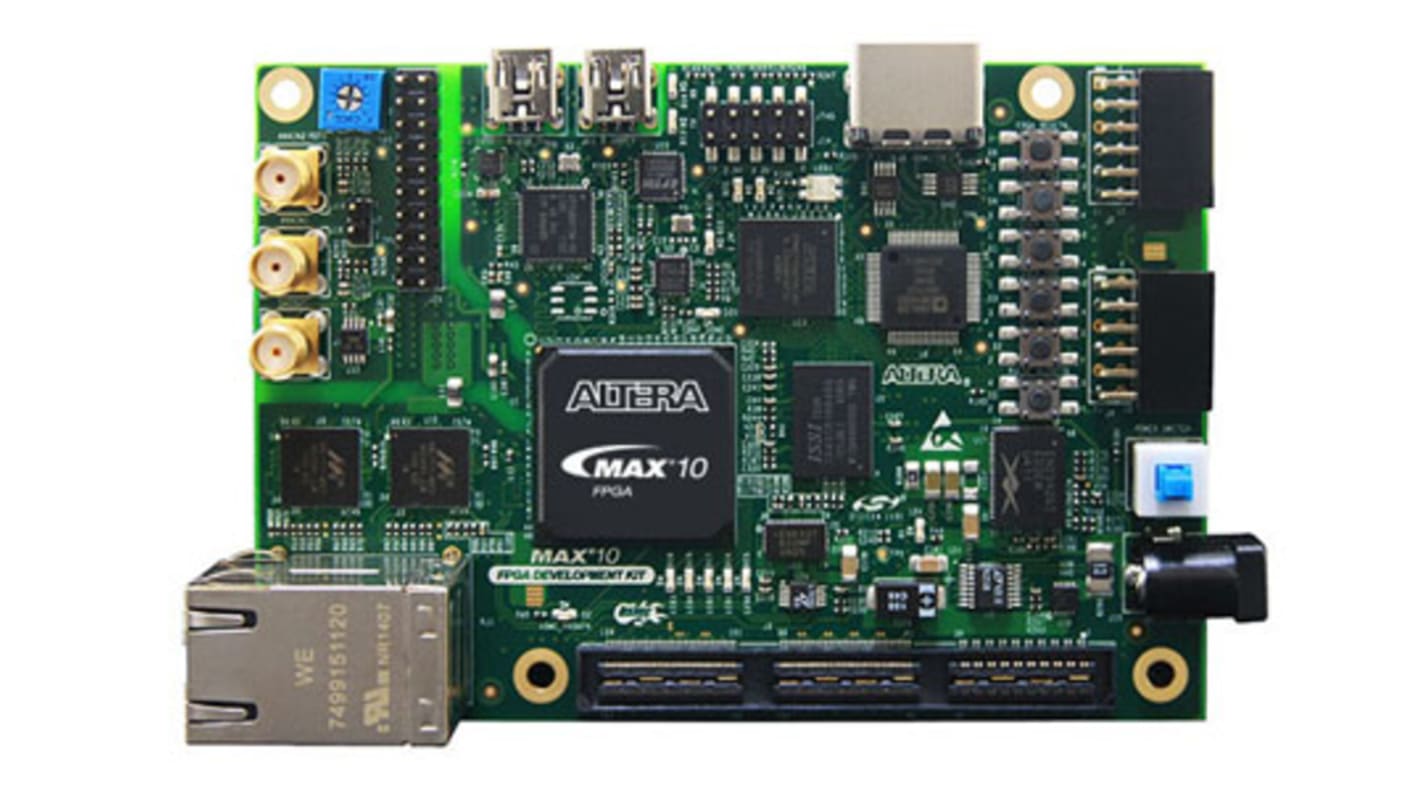

Le kit de développement FPGA Altera Max 10

Le kit de développement FPGA Altera MAX 10 est une plate-forme de conception complète construite autour d'éléments logiques (LE) 50 K. Il est optimisé pour l'intégration au niveau système avec ADC sur matrice, flash à double configuration et prise en charge d'interface de mémoire DDR3. Il dispose d'une gamme d'options de connexion telles qu'un USB-Blaster II intégré, une sortie HDMI et deux ports Ethernet pour les applications Ethernet industrielles. Le kit de développement FPGA MAX 10 fournit une solution de prototypage de niveau système pour les applications industrielles, automobiles et grand public.

Avec le kit de développement FPGA Altera MAX 10, vous pouvez :

Avec le kit de développement FPGA Altera MAX 10, vous pouvez :

- Développer des conceptions pour le FPGA 10M50D à boîtier F484

- Mesurer les performances du bloc de conversion ADC FPGA MAX 10

- Connecter les FPGA MAX 10 à une mémoire DDR3 à 300 MHz

- Exécuter un système Linux embarqué à l'aide du processeur Nios II

- Connecter des cartes-filles et des périphériques à l'aide de connecteurs compatibles HSMC et Digilent Pmod

- Mesurer la puissance du FPGA à l'aide de l'interface graphique utilisateur (GUI) du moniteur de puissance

- Réutiliser la carte de circuit imprimé et le schéma comme modèle pour votre conception

Programmation et configuration

- USB-Blaster II intégré (JTAG)

- JTAG direct en option via une embase à 10 broches

Périphériques mémoire

- SDRAM DDR3 1 Go 64-Mx16 avec contrôleur de mémoire souple

- SDRAM DDR3 1 Go 128-Mx8 avec contrôleur de mémoire souple

- Flash à quadruple interface périphérique série (SPI) 512 Mo

Ports de communication

- 2 ports Gigabit Ethernet RJ-45

- UART Mini-USB 2.0

- Sortie vidéo HDMI

- Connecteur de carte mezzanine ultra-rapide (HSMC) universel

- 2 connecteurs compatibles Digilent Pmod 12 broches

Analogique

- 2 entrées SMA d'ADC FPGA MAX 10

- 2 x 10 embases d'ADC

- Entrée de potentiomètre vers l'ADC

- DAC 16 bits externe avec sortie SMA

Horloges

- Générateur de signaux d'horloge à oscillateur externe 25 MHz à extrémité simple

- Générateur d'horloge Silicon Labs

Fourni avec

- Câble Mini USB pour USB-Blaster II intégré

- Alimentation et câble 2 A

- Logiciel de conception Quartus II Web Edition gratuit

- Mesurer les performances du bloc de conversion ADC FPGA MAX 10

- Connecter les FPGA MAX 10 à une mémoire DDR3 à 300 MHz

- Exécuter un système Linux embarqué à l'aide du processeur Nios II

- Connecter des cartes-filles et des périphériques à l'aide de connecteurs compatibles HSMC et Digilent Pmod

- Mesurer la puissance du FPGA à l'aide de l'interface graphique utilisateur (GUI) du moniteur de puissance

- Réutiliser la carte de circuit imprimé et le schéma comme modèle pour votre conception

Programmation et configuration

- USB-Blaster II intégré (JTAG)

- JTAG direct en option via une embase à 10 broches

Périphériques mémoire

- SDRAM DDR3 1 Go 64-Mx16 avec contrôleur de mémoire souple

- SDRAM DDR3 1 Go 128-Mx8 avec contrôleur de mémoire souple

- Flash à quadruple interface périphérique série (SPI) 512 Mo

Ports de communication

- 2 ports Gigabit Ethernet RJ-45

- UART Mini-USB 2.0

- Sortie vidéo HDMI

- Connecteur de carte mezzanine ultra-rapide (HSMC) universel

- 2 connecteurs compatibles Digilent Pmod 12 broches

Analogique

- 2 entrées SMA d'ADC FPGA MAX 10

- 2 x 10 embases d'ADC

- Entrée de potentiomètre vers l'ADC

- DAC 16 bits externe avec sortie SMA

Horloges

- Générateur de signaux d'horloge à oscillateur externe 25 MHz à extrémité simple

- Générateur d'horloge Silicon Labs

Fourni avec

- Câble Mini USB pour USB-Blaster II intégré

- Alimentation et câble 2 A

- Logiciel de conception Quartus II Web Edition gratuit

Circuits présentés

Un FPGA est un dispositif à semi-conducteurs composé d'une matrice de blocs logiques configurables (CLB) connectés par des interconnexions programmables. L'utilisateur détermine ces interconnexions en programmant la mémoire SRAM. Un CLB peut être simple (portes AND, OR, etc.) ou complexe (un bloc de RAM). Le FPGA permet d'apporter des modifications à une conception même après le soudage du dispositif sur un circuit imprimé.

Caractéristiques techniques

Attribut | Valeur |

|---|---|

| Technologie de logique programmable | FPGA |

| Classification du kit | Kit de développement |

| Nom du kit | MAX 10 |

- Code commande RS:

- 906-3924

- Référence fabricant:

- DK-DEV-10M50-A

- Marque:

- Altera