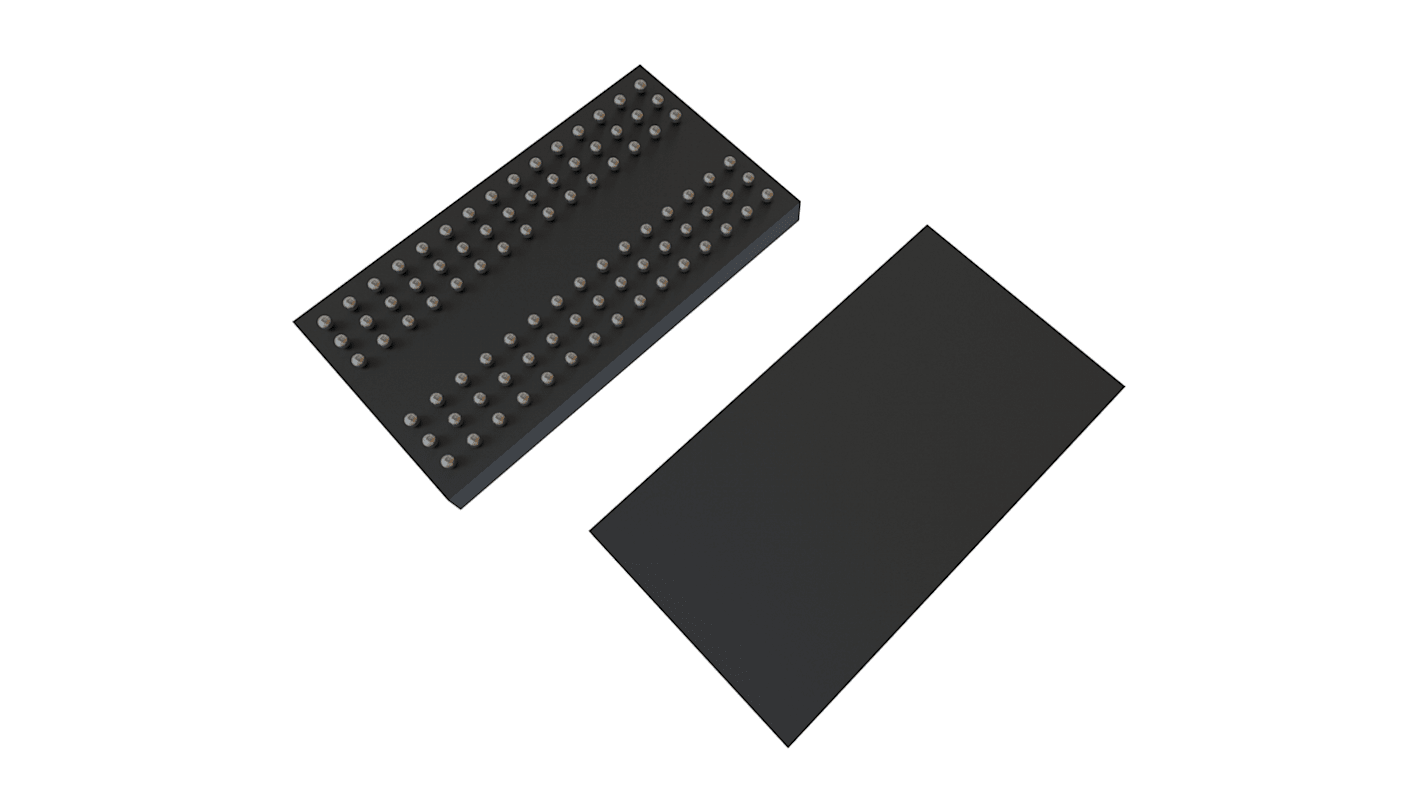

DDR2 SDRAM Winbond, 128 MB Surface 16 bit 95 °C -40 °C 84 broches, TFBGA

- Code commande RS:

- 188-2730

- Référence fabricant:

- W9712G6KB25I

- Marque:

- Winbond

Prix dégressifs sur quantité

Sous-total (1 paquet de 5 unités)*

11,16 €

HT

13,39 €

TTC

Frais de traitement offerts pour les commandes supérieures à 50,00 €

Temporairement en rupture de stock

- Expédition à partir du 24 août 2026

Besoin de plus? Cliquez sur " Vérifier les dates de livraison " pour plus de détails

Unité | Prix par unité | le paquet* |

|---|---|---|

| 5 - 5 | 2,232 € | 11,16 € |

| 10 - 15 | 2,03 € | 10,15 € |

| 20 - 45 | 1,992 € | 9,96 € |

| 50 - 95 | 1,968 € | 9,84 € |

| 100 + | 1,766 € | 8,83 € |

*Prix donné à titre indicatif

- Code commande RS:

- 188-2730

- Référence fabricant:

- W9712G6KB25I

- Marque:

- Winbond

Caractéristiques techniques

Documentation technique

Législation et Conformité

Détail produit

Recherchez des produits similaires en sélectionnant un ou plusieurs attributs.

Sélectionner tout | Attribut | Valeur |

|---|---|---|

| Marque | Winbond | |

| Type de produit | DDR2 SDRAM | |

| Taille de la mémoire | 128Mo | |

| Largeur de bus de données | 16bit | |

| Largeur de bus d'adresse | 15bit | |

| Nombre de bits par mot | 8 | |

| Temps d'accès aléatoire maximum | 0.4ns | |

| Nombre de mots | 16M | |

| Type de montage | Surface | |

| Type de Boitier | TFBGA | |

| Nombre de broches | 84 | |

| Température minimum de fonctionnement | -40°C | |

| Température d'utilisation maximum | 95°C | |

| Hauteur | 0.8mm | |

| Longueur | 12.6mm | |

| Normes/homologations | RoHS | |

| Série | W9712G6KB | |

| Tension d'alimentation maximum | 1.9V | |

| Standard automobile | Non | |

| Tension d'alimentation minimum | 1.7V | |

| Courant d'alimentation | 135mA | |

| Sélectionner tout | ||

|---|---|---|

Marque Winbond | ||

Type de produit DDR2 SDRAM | ||

Taille de la mémoire 128Mo | ||

Largeur de bus de données 16bit | ||

Largeur de bus d'adresse 15bit | ||

Nombre de bits par mot 8 | ||

Temps d'accès aléatoire maximum 0.4ns | ||

Nombre de mots 16M | ||

Type de montage Surface | ||

Type de Boitier TFBGA | ||

Nombre de broches 84 | ||

Température minimum de fonctionnement -40°C | ||

Température d'utilisation maximum 95°C | ||

Hauteur 0.8mm | ||

Longueur 12.6mm | ||

Normes/homologations RoHS | ||

Série W9712G6KB | ||

Tension d'alimentation maximum 1.9V | ||

Standard automobile Non | ||

Tension d'alimentation minimum 1.7V | ||

Courant d'alimentation 135mA | ||

Le W9712G6KB est une SDRAM DDR2 128 bits et une vitesse impliquant -25, 25I et -3.

Architecture à double vitesse de transmission : deux transferts de données par cycle d'horloge

Latence CAS : 3, 4, 5 et 6

Longueur du train d'ondes : 4 et 8

Strobes de données différentielles bidirectionnels (DQS et /DQS) transmis ou reçus avec des données

Bord aligné avec lecture de données et centre aligné avec écriture de données

DLL aligne les transitions DQ et DQS avec l'horloge

Entrées d'horloge différentielle (CLK et /CLK)

Masques de données (DM) pour écriture de données

Les commandes entrées sur chaque bord CLK positif, les données et le masque de données sont référencées aux deux bords de /DQS

Latence additive programmable /CAS prise en charge pour rendre l'efficacité du bus de commande et de données

Latence de lecture = latence additive plus latence CAS (RL = AL + CL)

Réglage de l'impédance du pilote hors puce (OCD) et terminaison intégrée (ODT) pour une meilleure qualité de signal

Fonctionnement de la précharge automatique pour lire et écrire des trains d'ondes

Modes actualisation automatique et autoactualisation

Mise hors tension préchargée et mise hors tension active

Masque de données d'écriture

Latence d'écriture = latence de lecture - 1 (WL = RL - 1)

Interface : SSTL_18